陕西黄河集团设计所 陕西西安 710043

摘要:本文涉及雷达信号处理领域,主要描述一种高速、实时数据转发录取技术,可以对系统性能和算法正确性进行事后分析验证,能够大大降低系统调试难度、减少开发周期。

前言:信号处理系统是对雷达接收到的回波信号进行A/D正交采样、数字下变频、抽取滤波等预处理,并进行MTI、MTD、FFT、谱分析、CFAR、过门限检测、和差归一化、抗干扰等处理,随着 数据吞吐率非常高、处理运算量非常大,相应的调试难度也越来越大,急需一种高速、实时数据转发录取技术,可以将采样数据实时录取存储,事后对信号处理系统预处理后的数据进行检查,用仿真软件对数据进行算法验证和优化,将优化后的算法移入信号处理系统中进行系统验证,大大提高调试效率。

以某型雷达为例,信号处理系统主要由和路、高低路、方位路、辅助路4路A/D模数转换模块进行模数转换、FPGA大规模可编程逻辑器件进行数字下变频、正交转换、滤波、抽取等预处理,多片DSP数据处理器进行数字信号处理计算。

其工作流程为:

上位机根据雷达工作模式,形成采样通道数、采样起始、采样长度、采样数据率、滤波器带宽等控制参数并发送给FPGA;

FPGA根据DSP形成的控制参数,对A/D采样后的数据进行通道选择、长度截取、抽取滤波等处理,形成后续处理所需要的I/Q数据,通过链路口总线或SRIO总线发送给由多片DSP模块组成的数字信号处理阵列;

DSP阵列对接收到的I/Q数据进行脉冲压缩、MTI/MTD、FFT、求模、非相干积累、CFAR检测、目标区分、和差归一化等。

在这种架构的信号处理系统中要实现原始数据录取有三种方法:

DSP阵列通过链路口总线或SRIO总线直接向存储设备发送数据,其优点是发送部分集成在DSP阵列,硬件不增加设备,缺点是发数逻辑集成在DSP阵列的工作软件中,对软件正常工作会有一定影响,存储部分要与DSP阵列安装在一个机箱中,对系统正常工作会有一定影响;

由上位机通过PCI总线控制FPGA访问DSP内存,将读取到的数据转存到存储设备,其优点是灵活性高,可根据需要选择数据区查看核录取。缺点是设计复杂度高,且会占用总线,存储部分要与DSP阵列安装在一个机箱中,对系统正常工作会有一定影响;

由FPGA直接将数据通过光纤发送给存储设备,其优点是发送逻辑集成在FPGA内,FPGA并行处理模式不影响工作状态,存储设备可独立于系统设计为便携手提式,使用时架设在制导站外,通过光纤与发送端连接,支持热插拔,传输速率高、传输距离远、抗干扰能力强,存储设备只接收数据,不向系统发送任何数据,不会对系统正常工作产生影响。缺点是发送端硬件需要增加光电转换模块,FPGA需要消耗一定资源实现发送逻辑。

综合考虑,第三种相对于前两种方法,硬件设计简单、使用方便、最重要的是对制导站正常工作不会产生任何影响,而增加的硬件和FPGA资源代价很小,因此选择此种方法。

首先,硬件电路上只需要增加一块光电转换器件,用于将需要记录的雷达信号处理系统原始数据转换为光信号。光电转换器件总线和FPGA可编程逻辑器件相连,由FPGA模块控制数据发送。以雷达数据率最高的模式为例,采样频率20MHz,数据格式为32位浮点I/Q,采样通道为4路,可以计算得出数据传输瞬时带宽为640MB/s,只需选用1路速率10Gbps的光电转换器就能够满足系统所有模式下的数据录取;

其次,FPGA程序保持原工作通道不变,只需要增加一个光口控制模块和雷达信号处理系统光口发送模块,光口控制模块按照所选光电转换器件手册进行配置和编码,光口发送模块的工作原理为:当FPGA程序判断到向DSP阵列发送控制数据或原始I/Q数据时,将这些数据同时由光口发送模块发送到光电转换器件,光电转换器件将数据转换成光信号发送到存储设备。

存储设备硬件部分包含光电转换板卡、存储硬盘阵列、主控PC板,光电转换器将光信号还原为电信号,主控PC机通过软件控制启动和停止将还原后的数据存储到硬盘中,还可以通过软件对存储的数据进行提取、状态判断、数据筛选、信号处理计算等仿真验证。数据录取构成框图见下图。

数据录取构成框图

光电转换板卡与主控PC板卡之间采用133MHz、64bit的PCI-X总线。主控板与磁盘阵列之间采用SATA 64Gbit/s串行总线,相较于传统的PATA并行总线,SATA总线使用嵌入式时钟信号,可以对传输数据和传输指令进行检查,如果发现错误会自动矫正,具备更强的纠错能力,且支持热插拔,在部分磁盘损坏的情况下也可以使用,最大程度的保证了存储数据的正确性和可靠性。磁盘阵列采用8块存储容量为1.5TB的硬盘,考虑到采样占空比及其他时序的低采样率,12TB的磁盘阵列可以保证连续记录时间超过24小时。

存储设备软件部分包含数据存储控制软件、波形回放软件、信号处理仿真软件。

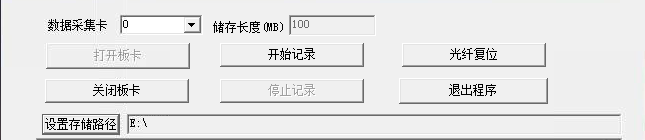

数据存储控制软件控制存储设备开始/结束录取,并在磁盘阵列形成数据文件,界面如下图所示。

数据存储控制软件界面

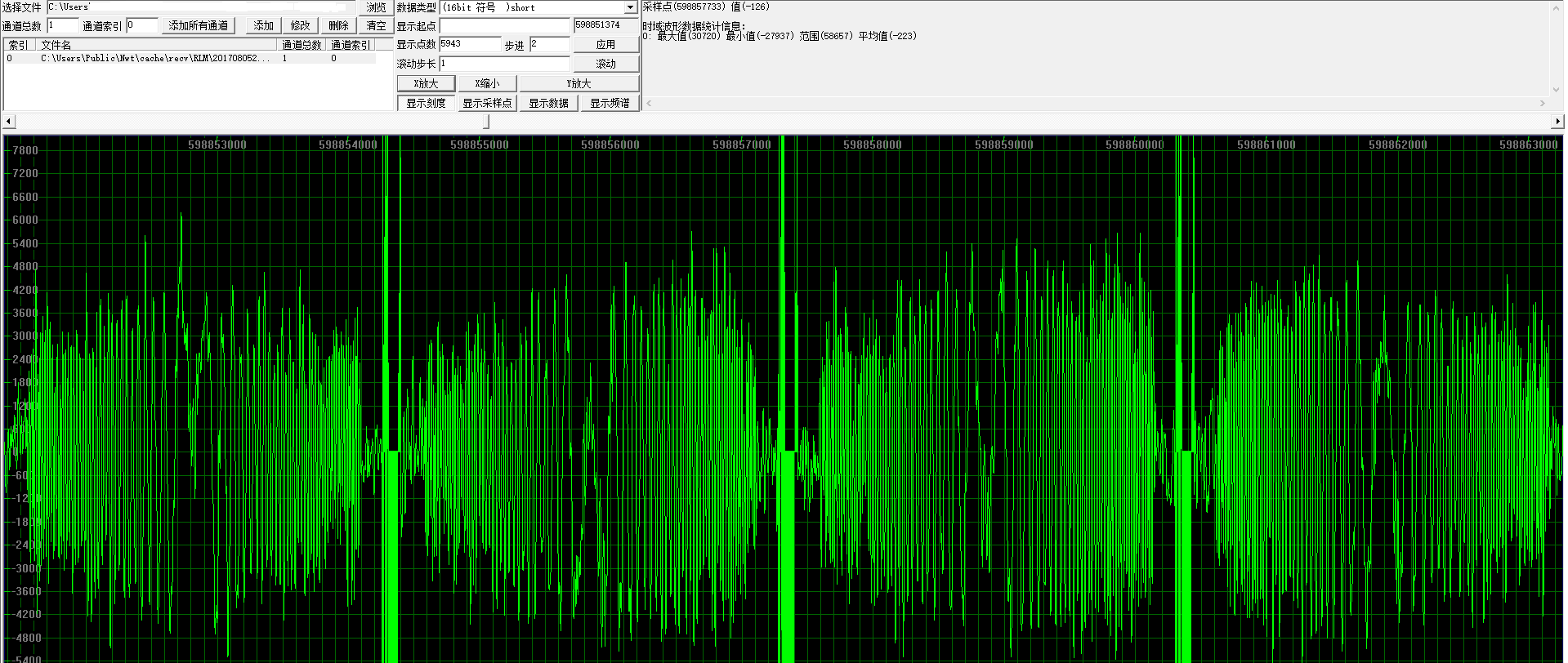

波形回放软件能够对已录取的数据文件进行回放,并且可以通过软件对回放数据区、回放信号通道、显示区横轴/纵轴尺度等进行设置,以精细显示用户所关注的信息,界面如下图所示。

波形回放软件界面

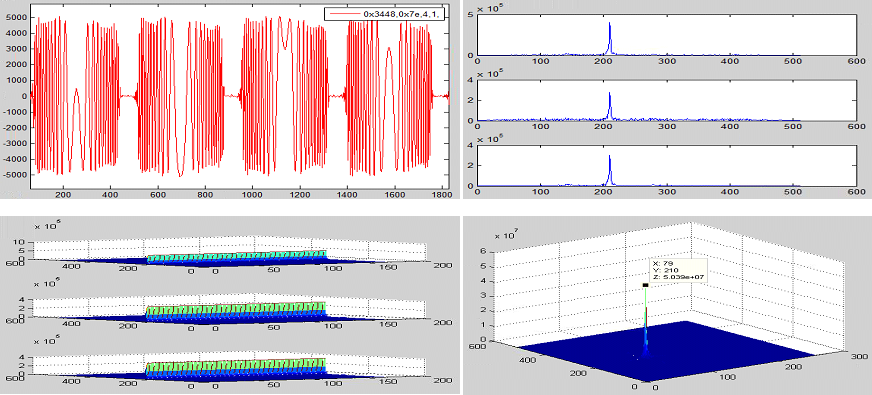

信号处理仿真软件是基于Matlab的数据处理及算法仿真软件,能够对录取到的数据进行事后处理,分析信号中的目标及干扰信息,验证目标处理算法和抗干扰措施的有效性,界面如下图所示。

信号处理仿真软件界面

结语:雷达原始信号的录取对于信号处理系统来说非常重要,绝大多数雷达信号处理系统在设计时都会考虑数据录取问题,在系统调试尤其是雷达整体调试、各种抗干扰试验和演戏对抗试验时,都要用到录取设备将试验环境下的雷达信号记录存储,事后进行仿真分析及效果评估,因此,如何根据雷达信号处理系统的架构设计一种结构简单、使用方便、与工作状态耦合小的记录存储设备,是值得深思和研究的。

参考文献

1.《雷达手册》 Merrill I.Skolnik 主编 电子工业出版社 2003年

王军 林强 米慈中 许绍杰 俞志强 武文等译

2.《信号与系统》于慧敏 主编 化学工业出版社 2002年