江南机电设计研究所,贵州贵阳550009

摘要:随着FPGA的高层次综合技术愈发成熟,在大多数实际中在不同的模块中同时出现错误的概率比较低,故TMR的应用前提与大多数实际情况相吻合,并且TMR的实现过程比较直接、简单,因此,TMR成为当前比较有效且使用广泛的缓解SEU的方法。下面本文就FPGA三模冗余工具的关键技术进行简要分析。

关键词:FPGA;三模冗余工具;关键技术;

1 TMR工具的发展概述

当前FPGA的TMR工具的发展主要集中在RTL阶段,无论是基于RTL描述还是基于RTL综合,类型多样,发展成熟。而新兴的基于HLS的TMR工具伴随着高层次综合技术的发展也在逐渐浮现,初出茅庐,前景广阔。这也是当前FPGA基于RTL的编程技术与基于HLS的编程技术的缩影,此外,针对特殊资源(如软核)的局部TMR优化也是一些FPGA设计工具的附加点工具的研究方向。FPGA三模冗余工具的发展依托FPGA的编程技术的发展。在RTL阶段进行三模冗余的设计,符合当前的FPGA编程技术仍是以硬件工程师进行RTL开发为主的现状,无论是基于RTL综合的TMR工具,还是基于RTL描述的TMR工具,都结合了相应的FPGA编程软件来进行实现,从而完成了对TMR电路的实现与各种性能微调,但是这种方法也将逐渐面临设计周期过长、复杂度过高等许多问题。集成电路随着摩尔定律发展至今,其复杂性已经逐渐超过人类可以手工管理的范畴,完全使用RTL级的逻辑抽象设计当代芯片是不现实的。在这种情况下,以占用3倍资源为基本思想的三模冗余更会大幅增加设计规模与复杂度,现有的RTL级三模冗余工具将会面临设计周期冗长、关键路径过长、资源占用过大等设计问题。此外,GPU之所以在人工智能时代取得了非凡成功,很大程度上得益于对软件和算法工程师友好的编程语言和环境。与之相比,FPGA虽然也在不断扩展自己的应用范围,并在性能和功耗上相比GPU有着明显优势,但其编程方法还是以硬件工程师进行RTL开发为主,这也是当前主流FPGA三模冗余工具仍集中在RTL级的主要原因,也是制约FPGA的大范围推广与使用的主要障碍。

2 TMR工具的关键技术

2.1 细粒度TMR技术

通常讨论的TMR是指将整个系统冗余3份的粗粒度方法,这种方法在SEU, SET发生频率较高的情况下,几乎发挥不了作用,故出现了一种在设计中将TMR本地化的方案,通过将设计的每一部分在局部进行3倍化与表决,从而掩蔽局部错误,提高系统在多错误情况下的可靠性。这种将设计以细粒度的方式应用TMR称为细粒度TMR技术,根据三模化的程度不同,将TMR分为局部TMR(Local TMR, LTMR)、分布式TMR(Distributed TMR, DTMR)、全局TMR(Global TMR)和块TMR(Block TMR, BT-MR)。LTMR是为了纠正出现在触发器中的SEU,将设计中的触发器均冗余为3份,并在其输出端添加表决器来进行表决,输入数据、控制信号和时钟均由冗余触发器共享,如图1所示,由于没有对组合逻辑单元、全局和复位进行冗余,这种方法不能为时钟信号、复位信号以及数据路径中的SET提供保护。在LTMR中,最主要的影响因素是潜在的SET,这些SET可能会通过影响触发器或通过触发器传播改变其状态来导致SEU,由于3个冗余的触发器共享1个数据路径,故发生在数据路径的任何一个SET都可以影响到3个冗余的触发器,从而导致表决失败。DTMR是除全局时钟和复位信号外,将设计中所有的组合逻辑单元、触发器和表决器都冗余为3份,从而屏蔽了SET对数据路径的影响,如图1所示,但是由于时钟仍是单一的信号,故时钟布线中的SEU仍会对设计产生影响。此外,当使用复杂的FPGA时,通常存在共享布线资源的组件,粒子对共享布线资源的干扰可能会导致两个TMR域同时出错,从而导致缓解策略的失败。GTMR是将设计中的所有组合逻辑单元、触发器、表决器和全局信号都冗余3份,如图1所示。

图1

通过3个时钟域与3个TMR域来保护电路不受SEU和SET的影响,但是GTMR的功耗和面积占用非常严重。而且,由于3个时钟域的存在,域的布局位置和时钟偏差都是需要解决的问题。BTMR是将包含组合逻辑单元和触发器的复杂函数视为黑盒,将整个块冗余为3份,多数表决器放置在3个冗余块的输出端,如图1所示,通常用来对从第3方购买且不能由用户编辑的IP模块添加三模冗余,但是其本质更接近于粗粒度TMR方法,无法为IP模块提供细粒度TMR的优点。不同粒度的TMR策略都有自身的优缺点与适用对象,LTMR占用资源较少,但是仅对触发器进行TMR,容错效果较差;DTMR资源占用与容错效果相对比较平衡;而GTMR牺牲了巨额资源换取容错效果;BTMR是一种对IP的妥协策略。此外,他们共同的缺点是缺乏对共享布线资源的容错。在使用复杂的FPGA时,通常会存在共享布线资源的冗余模块,而共享的布线资源遭受干扰时,常常会导致多个模块故障,常用的方法是将冗余模块布局在相距较远的位置,但是这也需要权衡,因为过远的距离意味着更多的线网资源以及潜在的关键路径延长,所以仍需探索如何对共享资源的优化。

2.2 系统分级技术

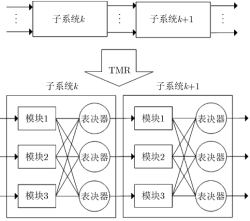

系统分级技术是为了缓解TMR仅容错不修复的缺陷,尽可能地扩展TMR系统的容错能力的一种手段。在分级技术中,整个系统首先被分解从成多个子系统,每个子系统执行系统的一部分任务,这些子系统被链接在一起形成系统。将TMR应用于分解的系统时,每个子系统都由3个冗余模块组成,每个子系统的输出在传播到下一个子系统之前都会进行表决,如图2所示。通过使用分级,在大多数情况下,即使在多个子模块出现故障的情况下,系统也可以保持正常运行。在普通的TMR中,一旦多个模块出现故障,系统就会出现故障,而在使用分级的TMR中,只要故障不发生在同一分级,系统就不会出现故障。

图 2 将TMR应用于分解的系统

2.3 配置刷新技术

TMR由于其仅容错不修复的缺陷,当某一模块出错后,电路仅通过表决器将错误屏蔽,但模块中的错误仍然存在,故在电路中会产生错误积累。由于错误积累的存在,TMR虽然可以在一定时间内大幅提高电路的容错能力,但是超过一定的错误积累之后,电路的容错效果会下降,从而导致电路的平均无故障时间(Mean Time To Failure, MTTF)降低。所以,为了更好地发挥TMR的优势,提高TMR电路的MTTF,需要将TMR电路与配置刷新结合,以纠正设备配置存储器中的错误。配置刷新是一种用于纠正FPGA配置存储器中错误的技术。刷新的目的是纠正电路中的静态组件,通常是LUT的内容以及布线情况等。

2.4 状态同步技术

伴随着SEU的发生,电路的状态也容易受到损坏。当配置刷新与含有带反馈时序逻辑的TMR设计一起使用时,对于触发器的状态同步是必不可少的。状态同步的目的是在通过配置刷新修复了FPGA的逻辑错误后,恢复其寄存器至正确的状态。同步电路的最常用方法是在电路的所有反馈环路上放置表决器,在反馈路径中的表决器可以确保电路之间的状态实时同步。

结束语

综上所述,SRAM型FPGA在宇航用电子设备中的应用越来越广泛,也使其容易受到单粒子效应干扰的问题更加凸显。TMR是当前比较有效且使用广泛的缓解单粒子效应的方法,众多学术机构与工业厂商均投入开发了为FPGA实现TMR设计的工具。

参考文献:

[1] 刘彤.FPGA三模冗余工具的关键技术探究[J].电子世界. 2016(19).166-168.

[2] 华成英,童诗白.FPGA三模冗余工具的关键技术分析 [M]. 高等教育出版社(第五版),2015.07.157-158.

[3] 刘彤.谢永超 汪科.基于 ARM 和 Zigbee 无线传输技术的远程温度监控系统的设计与实现 [J]. 单片机与嵌入式系统应用,2012.09.133-135.