贵州电子信息职业技术学院,贵州 凯里 556000

摘 要:现在均是使用集成门电路来设计组合逻辑电路,为了降低成本,提高电路的可靠性,实际设计时,应在满足要求的前提下,尽量减少所用芯片的数量和种类。通过对给定数字逻辑器件的情况下设计组合逻辑电路的方法进行研究。旨在提高广大电子爱好者化简逻辑函数的能力以及设计组合逻辑电路的能力。同时,也为数字电路实践教学提供参考课题。

关键词:全加器;卡诺图;设计;调试

基金项目:贵州省高层次创新人才培养项目-物联网技术及电子信息技术应用(黔千层人才[2015]05)

作者简介:

吴政江(1970-),男,本科,副教授,主要研究方向:电子信息工程技术、微波技术与物联网

中图分类号:TN918 文献标识码:A

0 引言

全加器、译码器是两个典型的组合逻辑电路,将二者结合起来并用显示器显示结果即可组成实际的数字逻辑电路。通过对数字逻辑电路实践教学课题“全加器显示器的设计与调试”的描述,说明在给定数字逻辑器件的情况下设计数字逻辑电路的方法与技巧。主要内容涉及逻辑代数、真值表、逻辑函数的化简、逻辑电路以及数字电路的安装与调试等。旨在提高广大电子爱好者化简逻辑函数的能力、设计组合逻辑电路的能力以及数字逻辑电路的综合应用能力。同时,也为数字电子技术实践教学提供参考课题。

1课题及要求

1.1 课题名称:全加器显示器的设计与调试。

1.2设计要求

(1)限用仪器及元器件:①数字电路实验箱限用1台;②SN7400或T095或T065(四-二输入与非门)限用5块;③共阴极七段字形显示器限用1块;④PC机(装有Proteus电路仿真软件)限用1台;⑤导线最多60根。

(2)输入:用三个逻辑开关K0~K2作逻辑符号输入,即用三个逻辑开关K0~K2代表三位二进制数。

(3)输出:用共阴极七段字形显示器显示三位二进制数和(全加和)的十进制数,即显示数字符号0~3。

(4)设计结果正确,显示器亮度适中。

2设计过程

2.1 核心器件介绍

SN7400或T095或T065为四-二输入与非门,是全加器显示器的核心器件,其引脚排列如图1所示。

2.2 具体设计过程

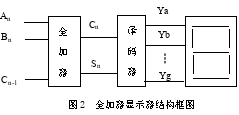

所谓全加器[1],是指3个一位二进制数相加的电路,其真值表如表1所示。其中An、Bn为本位二进制数,Cn-1为低位来的进位。实验中An、Bn与Cn-1分别用三个逻辑开关K2~K0代替。先用SN7400或T095或T065(四-二输入与非门)作全加器对3个开关信号K2~K0进行全加运算,输出为2位二进制数Cn、Sn(其中Cn为向高位的进位,Sn为本位和)。再用SN7400或T095或T065(四-二输入与非门)作字形译码器对Cn、Sn进行译码,最后用译码器输出驱动共阴极七段字形显示器显示符号0~3。其整个电路的结构框图如图2所示。

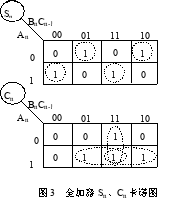

由表1可得Sn、Cn卡诺图如图3所示。由Sn、Cn的卡若图图可得Sn、Cn的逻辑表达式分别如(式1)和(式2)所示。由于SN7400或T095或T065是四-二输入与非门,所以应将全加器的输出Sn与Cn用摩根定理化简成二输入与非式的形式。又为减少元器件,应尽量找出Sn与Cn之间的公共部分。观察Sn与Cn的逻辑表达式,不难看出Cn有两个与非式![]() 与

与![]() 包含在Sn中,故Cn只需要2个二输入与非门。其他与非门与Sn共用。在Sn中,由于

包含在Sn中,故Cn只需要2个二输入与非门。其他与非门与Sn共用。在Sn中,由于![]() 出现两次,所以可节省3个二输入与非门,只需7个二输入与非门。若再加上An、Bn、Cn-1三个变量的反相器(将二输入与非门的两个输入端并联作反相器用),则全加器共需要2+7+3=12个二输入与非门。

出现两次,所以可节省3个二输入与非门,只需7个二输入与非门。若再加上An、Bn、Cn-1三个变量的反相器(将二输入与非门的两个输入端并联作反相器用),则全加器共需要2+7+3=12个二输入与非门。

表1 全加器真值表 | |||||

An(K0) | Bn(K1) | Cn-1(K2) | Cn | Sn | |

0 | 0 | 0 | 0 | 0 | |

0 | 0 | 1 | 0 | 1 | |

0 | 1 | 0 | 0 | 1 | |

0 | 1 | 1 | 1 | 0 | |

1 | 0 | 0 | 0 | 1 | |

1 | 0 | 1 | 1 | 0 | |

1 | 1 | 0 | 1 | 0 | |

1 | 1 | 1 | 1 | 1 | |

表2 字形译码器真值表 | |||||||||

Cn | Sn | Ya | Yb | Yc | Yd | Ye | Yf | Yg | 十进制数 |

0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 |

1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 3 |

字形显示译码器真值表如表2所示。由表2字形译码器真值表可得七段字形显示器各笔段逻辑表达式如下所示。

![]()

![]()

![]()

![]()

![]()

![]()

![]()

与全加器一样,由于SN7400或T095或T065是四-二输入与非门,所以应将译码器各段Ya~Yg用摩根定理化简成二输入与非式的形式。又为减少元器件,应尽量找出各段之间的公共部分以及各段之间的关系。由Ya~Yg的逻辑表达式可知,Ya、Yd相同,共用1个二输入与非门。Yb固定接高电平1,不需二输入与非门。 Yc需要1个二输入与非门。Ye为输入Sn的非,故不需要二输入与非门。Yf需要2个二输入与非门。Yg为变量Cn,不需要二输入与非门。故整个字形显示译码器只需要4个二输入与非门。加上变量Cn与Sn的反相器,整个字形显示译码器共需要4+2=6个二输入与非门。加上全加器的12个二输入与非门(将二输入与非门的两个输入端并联作反相器用),整个电路共需要

与全加器一样,由于SN7400或T095或T065是四-二输入与非门,所以应将译码器各段Ya~Yg用摩根定理化简成二输入与非式的形式。又为减少元器件,应尽量找出各段之间的公共部分以及各段之间的关系。由Ya~Yg的逻辑表达式可知,Ya、Yd相同,共用1个二输入与非门。Yb固定接高电平1,不需二输入与非门。 Yc需要1个二输入与非门。Ye为输入Sn的非,故不需要二输入与非门。Yf需要2个二输入与非门。Yg为变量Cn,不需要二输入与非门。故整个字形显示译码器只需要4个二输入与非门。加上变量Cn与Sn的反相器,整个字形显示译码器共需要4+2=6个二输入与非门。加上全加器的12个二输入与非门(将二输入与非门的两个输入端并联作反相器用),整个电路共需要

18个二输入与非门。5块SN7400或T095或T065(共有20个二输入与非门)足够了。

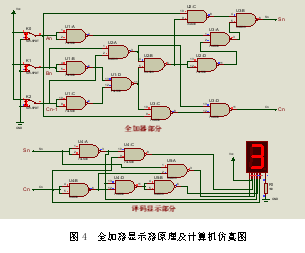

整个电路的逻辑原理图如图4所示。图中R1为限流电阻。其目的是避免因亮度太大而烧坏七段字形显示器内部的发光二极管。R1的阻值可按如下方法进行选取。TTL逻辑电路输出高电平电压通常为3.6V[2]。发光二极管(LED)的工作电压一般为1.5V~3.2V,取2V,驱动电流需几毫安至十几毫安,取10mA。则限流电阻R1可计算如下:![]() 。从而可选标称值为160Ω的电阻作为限流电阻。当然,也可以在Ya~Yg七段处各接一个限流电阻。

。从而可选标称值为160Ω的电阻作为限流电阻。当然,也可以在Ya~Yg七段处各接一个限流电阻。

从以上设计过程可看出,在用卡若图设计多输出组合逻辑电路时,首先需用摩根定理等公式将逻辑表达式化为所用器件的形式(如二输入与非式)。其次,为使所用的元器件最少,电路最简单,应尽量寻找各输出端的公共部分。此外,还应寻找各输出端的相互关系,如相等关系、包含关系等等。

3电路调试

3.1 计算机仿真调试

计算机仿真调试具有效率高、精度高、可靠性高和成本低等特点,已广泛应用于电路(或系统)的分析和设计中。计算机仿真不仅可以取代电路(或系统)的许多繁琐的人工分析,减轻劳动强度,提高分析和设计能力,避免因解析法在近似处理中带来的较大误差,还可以与实物试制和调试相互补充,最大限度地降低设计成本,缩短系统研制周期。可以说,电路的计算机仿真技术大大加速了电路(或系统)的设计和实验过程。鉴于此,全加器显示器在进行实物调试前先用计算机进行仿真调试。待仿真调试通过后再用数电实验箱进行实物调试。计算机电路仿真软件很多,而且各具特色。这里选用Proteus软件进行仿真。它是英国Lab Center Electronics公司出版的EDA工具软件,它不仅具有其它EDA工具软件的仿真功能,还能仿真单片机及外围器件[3]。用Proteus软件仿真全加器显示器显示3的结果如图4所示。

3.2数字电路实验箱调试

计算机仿真调试通过后,即可进行实物调试了。整个电路调试在数字电路实验箱上分三步进行。第一步,先调试全加器。在数字电路实验箱上用SN7400或T095或T065按图5上边全加器部分搭接全加器电路,并将其输出Cn、Sn分别连接两个LED指示灯。电路连接好后接通电源,并按表1改变K0~K2三个逻辑开关的逻辑状态,观察两个LED指示灯的亮灭情况。若两个LED指示灯的亮灭情况与表1相符,则说明全加器正确。第二步,再调试字形显示译码器。在数字电路实验箱上用SN7400或T095或T065按图5下边译码显示部分搭接字形显示译码器电路,并将其输入Cn、Sn分别连接两个逻辑开关。通电后拨动连接Cn、Sn的两个逻辑开关,若数码管的显示情况与表2相符,则字形显示译码器正确。第三步,最后将全加器与字形显示译码器连接进行统调。将全加器的两个输出端Cn、Sn与字形显示译码器的二个输入端Cn、Sn对应进行连接。通电后拨动K0~K2三个逻辑开关,观察数码管的显示情况。若显示情况与表1、表2相符,则整个电路正确。

4结束语

在给定逻辑器件的条件下设计组合逻辑电路,在分析给定问题,列出真值表后,应重点运用卡诺图及逻辑公式进行逻辑函数的化简。化简的目标不是求最简的逻辑表达式,而是求给定逻辑器件的表达式[4]。而且为了降低成本,提高电路的可靠性,实际设计时,应在满足要求的前提下,尽量减少所用芯片的数量和种类。这就必须寻找各输出端的公共部分。此外,还应寻找各输出端的相互关系,如相等关系、包含关系等等。文中以限用5块四-二输入与非门SN7400或T095或T065来设计全加器显示器为例,详细叙述了在给定逻辑器件的条件下设计组合逻辑电路的过程,并采用计算机仿真及实物两种方法进行调试。

参考文献

[1].李中发,胡锦,方厚辉,等. 数字电子技术[M]. 北京:中国水利水电出版社,2007.

[2].于晓平,庄宜松,李振东,等. 数字电子技术[M]. 北京:清华大学出版社,2006.

[3].吴政江,张定祥. 单片机原理及应用(基于C语言)[M]. 北京:化学工业出版社,2013.

[4].吴政江. 巧用卡诺图设计设计多输出组合逻辑电路[J] .电子世界,2011(9):10-12.