(伟乐视讯科技股份有限公司 广东 惠州 516003)

【摘要】在传统的数字电视系统的传输中,TS流的传输是严格按照CBR恒定码率传输的,基本不会引入突发。但随着IP网络的快速发展与普及,越来越多的TS流都承载在IP网络信道上传输。而IP网络众所周知天然存在网络拥塞,导致从IP网络信道上接收下来的IP包存在非常大的突发性。如果不做任何处理,将突发IP包中承载的TS直接送给数字电视处理设备,会导致数字电视处理设备无法正常工作。本文提出一种基于FPGA的TS平滑处理系统,对突发的TS流进行平滑处理,确保处理后的TS可以被数字电视处理设备正确处理。

【关键词】TS突发 TS平滑 网络拥塞

A TS Smoothing System Based on FPGA

YUAN Jinbao,HUANG Huaji, YANG Xuesong

(Wellav Technologies Ltd., Huizhou 516003, China)

Abstract: In the transmission of traditional digital TV system, TS stream is transmitted strictly in accordance with CBR constant bit rate, and burst is not introduced. However, with the rapid development and popularization of IP networks, more and more TS streams are carried on IP network channels. As we all know, the IP network is naturally congested, resulting in a very large burst of IP packets received from the IP network channel. If no processing is done, the TS carried in the burst IP packet is directly sent to the digital TV processing equipment, which will cause the digital TV processing equipment to fail to work normally. This paper proposes a TS smoothing system based on FPGA, which smoothes the burst TS stream to ensure that the processed TS can be correctly processed by the digital TV processing equipment.

Key words: TS Burst TS Smooth Network Congestion

1 引言

在传统的数字电视传输系统中,信源端编码出来TS码流都是CBR恒定码率的。编码后的流经过的传输网络也不存在网络拥塞,比如我们熟知的ASI传输网络,调制Cable传输网络等。基于此,绝大部分的数字电视处理前端设备和终端解码设备,都只能支持恒定码率的TS流。

随着IP网络的快速发展与普及,越来越多的TS流都承载在IP网络信道上传输,即TS Over IP。得益于IP组网的灵活性,通过TS over IP进行数字电视信号传输,变得非常地方便、高效与低廉;但随着业务量的剧增以及网路拓扑复杂度的提高,IP网络的拥塞也变得更加的突出。虽然在网络中各级交换机都会有自己的缓存来保证网络拥塞不造成IP包丢失,但是接收端收到的IP包则会形成突发,即一段时间内收到密集的包,而一段时间内则很少收到包。同样地从IP包中恢复出来的TS流也就不再是恒定码率。如果此种TS流不做任何处理送给数字电视系统处理设备,会导致数字电视系统处理设备无法正常工作。

2TS平滑处理系统的设计与实现

2.1 实现原理框图

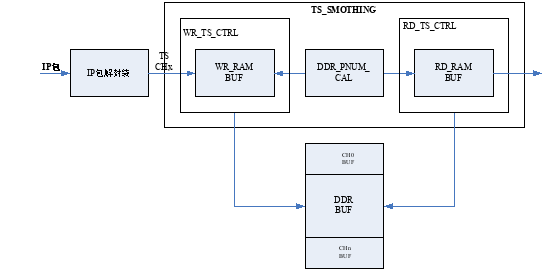

如图 1所示,IP包解封装模块实现IP包解封装,将IP包中承载的TS恢复出来。TS over IP一般都是通过IP地址加端口号组成一个IP通道,每个IP通道携带一路完整的TS流。因此,一个物理网络接口进来的IP包,可以带上多个通道。因此,IP包解封装模块会输出恢复出来的TS流,同时还设计一个对应的通道号来标志该TS流。

解封装后的TS会输出到TS平滑模块,如前文所述,TS平滑模块负责将突发的TS流进行平滑。其大致分为3个部分。WR_TS_CTRL、DDR_PNUM_CAL和RD_TS_CTRL部分。其中,WR_TS_CTRL将TS按通道依次将TS包写到DDR_BUF中进行缓存;RD_TS_CTRL模块负责将TS包从DDR_BUF缓存中读出来;DDR_PNUM_CAL负责统计在DDR_BUF中各个通道当前的TS包数。

图 1 TS平滑实现框图

图 1 TS平滑实现框图

2.2 内部详细设计

图 2 WR_TS_CTRL模块实现框图

在WR_BUF_RAM模块中,设置一个FPGA内部的简单双端口RAM,一般设置该RAM缓存32个TS包的深度。RAM的写端,处于CLK_IP时钟域。主要是将IP解封装模块输出的TS包和该TS包对应的通道号写入到该RAM中。在RAM的读端,处于CLK_DDR时钟域,统计RAM中实时的TS包数PNUM并送给WR_DDR_CTRL模块。对于PNUM的统计,涉及到一个读写时钟域的同步。在设计中,在写端写完一个包后产生一个WR_APCK_FINISH信号并拉高,持续20拍时才拉低,这样就可以将WR_APCK_FINISH信号通过最简单的打2拍的方式传递到读时钟域CLK_DDR。我们计为WR_APCK_FINISH_2D。在读时钟域,对打2拍的WR_APCK_FINISH作一个上升沿检沿,我们计为WR_APCK_FINISH_RD_P。此时,PNUM的计数则简化为:WR_APCK_FINISH_RD_P有效,加1;RD_TS_REQ有效,则减1。

WR_TS_CTRL模块检测到WR_BUF_RAM中的PNUM不为0,则先去读取TS包的通道号,获取通道号后就发一个GET_PNUM_DDR的请求,查询该通道在DDR_BUF中实时的包数。如果该通道在DDR_BUF中的缓存未满,则向DDR控制器发起写DDR请求WR_DDR_REQ。当DDR控制器能响应写请求时,则返回WR_DDR_ACK。此时,就可以向WR_RAM_BUF模块发起RD_TS_REQ读取TS包。并将读取到的TS包,写到通道号对应的DDR的缓存中。

WR_TS_CTRL模块已经将TS包按照通道缓存在DDR_BUF中,以何种速率从DDR_BUF读取,则是实现TS平滑的关键。

在TS流的传输中,为了确保音视频在编码端和解码端同步,协议规定每隔10ms~100ms需要在TS流中插入PCR包。而PCR包在编码端实现规则如下:在编码器中有一个系统27MHz时钟,用该时钟产生一个PCR计数器,该计数器由PCR_Ext和PCR_Bas组成。PCR_Ext为27MHz时钟进行模300计数分频,即计数器从0累加299,再回到0,获得9位二进制值。PCR_Ext每计数到299时,进行模233计数,获得33位计数值PCR_Bas。由此可知,PCR包本质上表征了该TS流的原始时间信息。因此只需要捕获2个连续PCR包并提取包中携带的PCR值,即可获得这2个连续PCR包在编码时的原始时间间隔。计为T=PCRn-PCRn-1;再统计这2个连续PCR包间隔内的包数PNUM,即可获得这个时间间隔内的TS的bit数。根据协议规定,TS包按照包长188字节传输,所以每个TS包bit数为188*8bit。计2个连续PCR包间的bit数为B=PNUM*8*188bit。由此,码率即可由以下公式计算得到。

Rate=B*27000000/((PCR_Basn-PCR_Basn-1)*300+(PCR_Extn- PCR_Extn-1))

when PCR_Extn> PCR_Extn-1

Rate=B*27000000/((PCR_Basn-1-PCR_Basn-1)*300+(PCR_Extn+300-PCR_Extn-1))

when PCR_Extnn-1

在设计实现中,设置一个FPGA的内部RAM。以通道作为RAM的地址,分别将PCRn,PCRn-1以及PNUM写入RAM中。软件定期来读取该RAM,即可按照文中公式,计算得到各个通道的读码率,然后以参数的形式下发到FPGA。考虑到实际应用场景中,PCR包中的PCR值偶有异常或者PCR包偶有丢失的可能,软件更新码率参数时,需要加以判断,将异常的PCR数据丢弃掉,也即不更新码率参数,FPGA保持之前的码率对DDR_BUF进行读取。

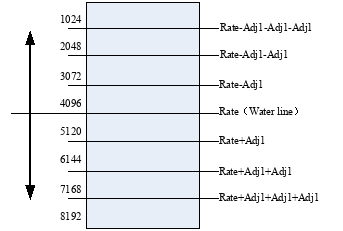

理论上,按照PCR计算到的码率去读取DDR的速率,读出来的TS流是可以恢复到编码端的恒定码率。但实际中,考虑到时钟频率的偏差以及FPGA将码率转换为读包间隔的误差,这个码率仍然有细微偏差的。这个偏差虽然非常的小,但是经过长时间的累积,会导致DDR_BUF出现包累积或者读空。因此,实际设计中需要根据DDR_BUF中的包数情况,对码率进行微调。如图 3所示,假定每个通道在DDR_BUF中设置了8192个包的缓存空间。系统启动后,当DDR_BUF中的包数到达4096时,按照PCR计算出的Rate启动TS包读取。运行一段时间后,如果DDR_BUF中的包数减少到3072时,说明计算出的Rate偏大,即读取速率大于写入速率,导致DDR_BUF中的包数在逐渐减少,FPGA会对Rate进行减小Adj1的调整。依次类推,根据缓存中的包数,对码率做对应的调整。随着码率的调整(减少),DDR_BUF的包数又会向4096的Water Line靠近;同理,DDR_BUF中包数累加情况则与之相反,说明计算出的Rate偏小,即读取速率小于写入速率,导致DDR_BUF中的包数在逐渐增加,码率对应的加上Adj1,最终的效果是DDR_BUF的包数同样向4096的Water Line靠近。

图 3 根据DDR_BUF包数码率微调示意图

RD_TS_CTRL整体实现框图 4所示,RATE_CAL模块负责将码率计算信息送给软件,软件计算好码率,以参数的形式下发给FPGA。FPGA根据各个通道的码率信息,产生各通道的读包请求存入CMD_FIFO中。一旦CMD_FIFO为空,则由RD_DDR模块根据CMD_FIFO信息发起读DDR_BUF的请求,同时根据DDR_PNUM_CAL中的包数,对读包码率进行微调。

图 4 RD_TS_CTRL实现示意图

对于超多通道的设计,比如1024个IP通道,如果按照WR_BUF_RAM模块的PNUM的方式设计,本模块将会占用大量的FPGA逻辑资源。本文提出了一种用RAM存读写指针来获取DDR_BUF包数的设计方法,可以实现FPGA资源的均衡利用。

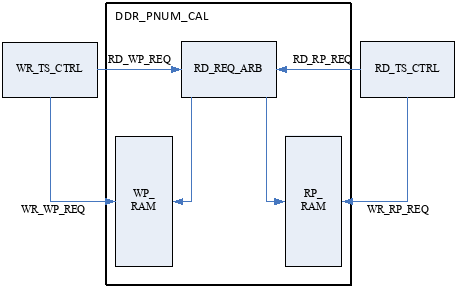

如图 5所示,在设计中,WP_RAM用来缓存写指针,RP_RAM用来缓存读指针,都统一按照通道来存储读写指针。先分析一下需要从本模块操作RAM的场景:

1)WR_TS_CTRL模块检测到WR_RAM_BUF有包时,此时需要先读取DDR_BUF中是否满了用以决定是否往DDR_BUF中写包,此时需要用待写包的通道号作为地址,读取WP_RAM和RP_RAM以获得PNUM。

2)当场景1)获取的PNUM未满时,DDR_BUF接收写DDR请求时,需要更新写指针。此时需要先读取WP_RAM,读取出来RAM中的写指针加1后再写入到WP_RAM中,以此完成写指针的更新。

3)RD_TS_CTRL模块根据软件下发的各通道码率产生各通道读包信息,并将读包信息存入CMD_FIFO中。CMD_FIFO不空时,则会从FIFO中取出读包信息,然后根据读包信息去DDR_BUF中读TS包。在实际读DDR_BUF之前,会先判断DDR_BUF是否为空用以决定是否要真正从DDR_BUF中读包。此时需要用待读包的通道号作为地址,读取WP_RAM和RP_RAM以获得PNUM。

4)当场景3)获取的PNUM未空时,DDR_BUF接收读DDR请求时,需要更新读指针。此时需要先读取RP_RAM,读取出来RAM中的写指针加1后再写入到RP_RAM中,以此完成写指针的更新。

从上述场景来看,场景1)存在读WP_RAM、RP_RAM;场景2)存在读WP_RAM,写WP_RAM。场景3)存在读WP_RAM、RP_RAM;场景4)存在读RP_RAM,写RP_RAM。场景1)和2)处于写DDR_BUF操作,是串行操作,同样场景3)和4)处于RD_DDR_BUF操作,也是串行,不存在读写冲突;但是写DDR_BUF和RD_BUF是独立操作,是会存在读操作冲突的。

图 5 读写指针双RAM实现示意图

2.3 调试与验证

搭建测试验证环境拓扑图如图 6所示,信源采用伟乐科技的HDMI编码器。该款编码器采用富士通的M22芯片进行编码,编码后流通过IP输出给到交换机。然后IP_QAM从交换机中取流,对IP流进行处理后通过调制QAMA输出,最终给到机顶盒STB解码以及sencore公司的VB分析仪进行监控。

图 6 测试系统框图

图 6 测试系统框图

测试结果:

1)打流器不开启,STB解码正常播放,无卡顿、无马赛克;分析仪监控290无错误,码率恒定。

2)打流器开启,Eth_switch设置QoS,使Eth_switch处于网络拥塞,此时VB监控Eth_switch输出的流,有TR290 PCR错误,码率有波动突发;IP_QAM未开启TS平滑,机顶盒出现播放卡顿、马赛克,分析仪上报TR290 PCR错误,监控到码率有波动突发;开启TS平滑后,STB正常播放,无卡顿、无马赛克;分析仪监控290无错误,码率恒定。

3 结论

本文分析了TS突发形成的原因以及对传统数字电视处理设备的影响,并详细介绍用FPGA实现TS流的平滑处理的方案以及设计实现。所述方案已成功应用到伟乐公司CMP等媒体平台设备中。在实际的客户IPTV应用场景中,当未开平滑功能,客户终端播放会出现卡顿、马赛克等异常情况。当打开平滑功能后,能立即恢复正常使用。实践证明本系统长时间稳定运行,平滑后的TS流送给终端解码,音视频正常播放,用码流分析仪长时间监控,均无290错误。

参考文献

[1]许春蕾.TS over IP传输技术在电视台的应用及展望 [J] . 现代电视技术. 2014,第004期

[2]方磊 赵想瑞 蔡世军 陈雨露 李敏.电视技术中音视频同步技术及实现.电视技术,2015

[3]洪飞 吴志美. MPEG-2 传送流传输方法的研究与改进. 计算机学报,2004.

[4]易湖 赵照 薛利军 刘运锋 高峻雄 王耘波 于军. DVB传输流PC R抖动检测的FPGA实现.中国有限电视,2005.