维沃移动通信有限公司 广东东莞 523000

[摘要]对手机产品开展产品级跌落的仿真分析,能够对模拟产品当中元器件处于跌落过程当中载荷状态予以有效模拟分析,反映产品处于跌落状态下各部件接触及其相互作用情况。因现阶段针对于手机结构的设计因子之下对产品级跌落可靠性所产生影响方面研究鲜少,为更进一步地完成跌落仿真,为手机产品总体生产质量提供保障,就还需增加对此此方面的深入研究。故本文主要探讨手机结构的设计因子对于产品级跌落可靠性所产生的影响,仅供业内相关人士参考。

[关键词]手机结构;产品级;设计因子;可靠性;跌落;影响

前言:

对手机开展产品级跌落的仿真分析,是保证手机产品总体结构设计制造质量及性能的重点工作。那么,若想确保跌落仿真能够有效可靠地实施,则对手机结构的设计因子对于产品级跌落可靠性所产生的影响开展综合分析较为必要。

1、模型构建

先借助三维建模系统,设计手机产品三维结构简易模型,并对结构予以合理简化。手机产品模型为74mm*162mm*8mm尺寸,PCB(印制的电路板)借由均匀布设6个螺钉妥善固定于壳体内。为合理简化模型,PCB上面芯片及其器件建模省略,仅对临近前壳位置将CSP模型构建起来。

2、影响分析

2.1在底填料方面

模型内部板载CSP封装体未设底填料,但产品当中常常会借助底填料,将PCB板和板级封装之间热及机械应力实际不匹配度降低,对应力集中起到缓解作用。通过对比分析有及无底填料条件之下,芯片与焊点之间最大的主应力情况后可了解到,对于焊锡占比比较大的芯片,如cpu,详见图1,这种封装尺寸下,底填胶的填充一方面增加了局部刚度减少pcb的变形,能够很大程度的降低焊锡的应力情况,同时本体相应的降低[1]。对于焊锡占比比较小的芯片,如ufs芯片,详见图2,这种芯片焊锡面积比芯片本体小很多,底填胶的填充依旧可以降低焊锡的应力,但是对于本体而言,则不一定能够起到降低应力的效果,原因有二,一则是对于ufs这种芯片而言,焊锡局部和pcb的变形相对比较协调,而没有焊锡的位置,则其本体和pcb变形协调程度较差,而底填胶的模量相对于焊锡而言低很多,无法较大程度改善这种协调情况,在这些区域增加底填胶就会强行将pcb的变形传递给本体,造成本体变形较大从而失效。另一个原因则是ufs这种封装芯片本体的受力主要是pcb通过焊锡传递到本体,由于焊锡范围较小,pcb中间局部的变形只会传递到局部,但是如果增加了底填胶,pcb上其他位置的变形也能通过底填胶直接传递给芯片本体,从而增加了芯片的受力区域,进而使得芯片的实效风险和概率增加。

图1 CPU示意图

图2 UFS示意图

2.2在螺钉间距方面

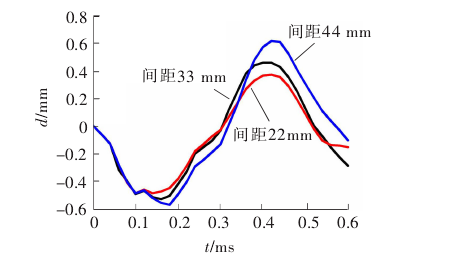

所构建模型当中,选取均匀分布的6个螺钉,把PCB妥善固定于手机整个壳体上面,中间螺钉至两侧螺钉维持33mm间距范围。中间螺钉,其和封装体最为接近落点相互间的间距,则为33mm(螺钉的一个基础间距范围)。中间的2个螺钉,则分别向着临近于封装体一侧及与封装体较远一侧移动约11mm,也就是螺钉间距各设定22mm及44mm。以此对不同螺钉间距执行,对于板级组装总体可靠性所产生影响进行分析[2]。经分析后了解到,因螺钉间距持续缩小,致使芯片与焊点之间最大的一个主应力呈降低趋势。螺钉间距由44mm逐渐缩小为22mm后,芯片部位最大的一个主应力则由184MPa下降至143MPa,总体降幅约22.30%。针对焊点部位最大的一个主应力,则由238MPa下降至183MPa,总体降幅约23.10%。为考察分析整个封装体位置PCB挠度(d)受不同螺钉间距条件之下产生影响情况,提取与该焊点3"角相距最近的PCB上面节点处于跌落过程当中位移曲线,减去外端部位螺钉固定H节点产生位移,获取PCB上面F节点一个挠度曲线,详如图3所示。由此便可了解到,封装体侧位置螺钉间距逐渐减小情况下,封装体所对应PCB部位挠度随之减小,芯片与焊点位置最大的一个主应力明显减小。

图3不同的螺钉间距条件之下F节点实际挠度变化曲线图

2.3在屏蔽框方面

手机产品当中,通常会借助屏蔽框,对PCB上面芯片封装及器件起到保护作用,防止静电干扰或碰撞冲击等所致功能失效情况出现。此次改变手机模型,对板载的CSP封装分别设定面积不同的3个屏蔽框,即15.00mm*15.00mm、12.00mm*12.00mm、9.00mm*9.00mm。屏蔽框越大面积条件之下,芯片与焊点之间最大的一个主应力就相对越小。相比较无屏蔽框,设15.00mm*15.00mm面积的屏蔽框条件之下,芯片部位最大的主应力由166MPa下降至136MPa,总体降幅约18.10%;而焊点部位最大的主应力由225MPa下降至166MPa,总体降幅约26.20%。如此可见,手机产品总体结构设计期间,对重要部件应设面积较大一个屏蔽框,便于对PCB上面芯片封装及器件起到一定的保护作用。此外,结合图4了解到,设屏蔽框后,F节点部位挠度可明显减小,屏蔽框越大面积之下,此点挠度就相对更小,芯片和整个焊点部位最大的主应力明显呈越小趋势。

图4屏蔽框不同面积条件之下F节点位置挠度的变化曲线图

2.4在芯片和前壳间隙方面

所构建模型当中,CSP封装整个芯片和前壳之间间隙为0.65mm,更改模型后,二者间隙则分别增加、缩小0.15 mm。芯片和前壳相互间呈较小间隙值条件下,可能有碰撞发生,致使封装体所产生冲击应力相对较大,封装体就会存在着过应力的失效风险。针对壳体与器件方面碰撞风险,往往可以结合芯片封装形式予以判断分析。对于玻璃封装的芯片,往往易碎,设计中不允许有较大撞击情况出现。而对于树脂封装的芯片,在满足装配要求的情况下,不会过多的要求其设计间隙值。甚至在很多的实际应用中,经常会在芯片和壳体之间增加软垫给予支撑。在pcb变形比较大导致芯片受力较大时,可以通过在在芯片上方增加支撑,从而变相的减少pcb的变形情况来降低芯片的受力。

3、结语

通过此次对手机结构的设计因子对于产品级跌落可靠性所产生的影响开展仿真分析,最终获取的结论详细如下:对于焊锡占比比较大的芯片,如cpu,这种封装尺寸下,底填胶的填充一方面增加了局部刚度减少pcb的变形,能够很大程度的降低焊锡的应力情况,同时本体相应的降低。对于焊锡占比比较小的芯片,如ufs芯片,这种芯片焊锡面积比芯片本体小很多,底填胶的填充依旧可以降低焊锡的应力,但是对于本体而言,则不一定能够起到降低应力的效果;同时,针对封装体侧位置螺钉间距逐渐减小情况下,封装体所对应PCB部位挠度随之减小,芯片与焊点位置最大的一个主应力明显减小;设屏蔽框后,F节点部位挠度可明显减小,屏蔽框越大面积之下,此点挠度就相对更小,芯片和整个焊点部位最大的主应力明显呈越小趋势;对于玻璃封装的芯片,往往易碎,设计中不允许有较大撞击情况出现。而对于树脂封装的芯片,在满足装配要求的情况下,不会过多的要求其设计间隙值。甚至在很多的实际应用中,经常会在芯片和壳体之间增加软垫给予支撑。pcb变形比较大导致芯片受力较大情况下,可对芯片上方位置增加支撑,促使pcb变形情况减少,以此达到降低芯片总体受力的目的。

参考文献:

[1]侯丽美,王大龙,游远萍,等.基于有限元仿真的结构可靠性影响因素分析[J].测控技术,2022,41(1):58-62.

[2]刘伟.影响手机结构设计的关键因素[J].数码世界,2019(3):158.