广州广电计量检测集团股份有限公司 广东 广州 510656

摘 要:在目前市场环境以及电动汽车的普及,SIC作为第三代功率半导体器件应用得更加广泛,其开关速度快、功率密度高和DS可以承受更大的直流电压,因此在航空航天、变流转换等方面,SIC功率器件在电力电子设备中起到电能转换的重要工作,故其对可靠性要求较高。本文以SiC MOSFET 为研究对象,并且根据AQG324标准设计动态栅偏检测电路并将阈值电压检测与动态栅偏结合,在动态栅偏中随时进行阈值电压的测试,并通过上位机进行采样保存,极大地提高了检测设备的多功能性。

关键词:动态栅偏;阈值电压;AQG324;上位机

1前言

在电力电子装置中,使用 SiC MOSFET 可以在控制中给栅极更高的频率,从而在电力电子设备中获得较低的THD,对电网的污染也相对更加微弱。SiC MOSFET在导通时需要承受大电流,在关断时可能承受较大的母线电压,若SIC无散热则可能导致其芯片的结温远高于环境温度,SiC MOSFET在高温下可能发生各种故障,不仅影响了电力电子设备的安全性,还会造成安全事故。SiC MOSFET芯片结温对其可靠性具有决定性的影响。

在Si C MOSFET中,阈值电压视不可或缺的参数。SiC MOSFET 的栅氧化层可靠性不如普通硅的可靠性,由BTI 引起的阈值电压漂移和任然需要更好的解决方案。因此,将动态栅偏与阈值电压相结合的方法对分析 SiC MOSFET 的可靠性有一定的参考价值。

2 动态栅偏的设计原理与方案

2.1 动态栅偏相关标准与原理说明

使用 Si C MOSFET 可以在控制中给栅极更高的频率,但是其GS相对于DS更加容易击穿引起失效,因此需要验证GS的稳定性,但是对于目前静态栅偏已经不能满足可靠性试验的要求,因为静态试验仅是在GS加入稳定的最大栅偏电压,并保持相应的时间,无法验证GS在实际工作环境条件下的可靠性,因为在高频的开通关断中,GS所承受的电应力与静态的条件下承受的电应力存在不同。因此在最新版的AQG324中详细列出了动态栅偏的要求与条件。目前详细的测试参数有略微不同,因为驱动程序的不同可能在测试中有略微差异。这个测试用于芯片级的同时亦可用于模块的可靠性研究。由于其布局的差异,模块设计对芯片级的实际VGS有影响。目前,DGS测试(动态栅偏)仅对碳化硅的可靠性进行试验。其实验条件如表2-1所示。

表2-1 动态栅偏推荐测试参数

Table 2-1 Recommended Test Parameters for Dynamic Gate Deviation

对于动态栅偏而言,其循环次数、温度、DS电压、频率、最大最小栅极电压等参数比较容易达到,但是其主要保证dgs/dt=1V/ns,此项要求比较难以控制,因此需要设计合理的驱动电路满足此项要求。对于栅极电阻选取一般有两个方案。一方面,减小栅极电阻的阻值,可以获得更高的开关速度。从而降低开关损耗而减小发热。另一方面,增加栅极电阻会减小开关速度,这可使栅极电路中发生的由寄生杂散电感或耦合电容引起的振荡减少。因此,需要通过实验获得最佳的栅极电阻阻值。但是对于动态栅偏实验而言,可能存在不论如何调节栅极电阻都无法达到1V/ns的情况,因此需要其他方案进行优化。

使用一个栅极驱动可能无法满足要求,在此将两个驱动并联输出便可达到要求,其原理如图2-1所示。

图2-1 驱动原理图

Figure 2-1 Drive Principle Diagram

在此通过两个驱动芯1EDC60H12AH并联输出进行驱动,芯片1EDC60H12AH为英飞凌开发的为SIC器件设计的专用驱动芯片,其可以输出高达10A一个典型的峰值电流,使用光耦的方案进行隔离,适合在UL 1577条件的高环境温度下运行,绝缘测试电压为VISO=3000V/秒,通过将芯片的输入IN+同时接入PWM信号,IN-选择接地与单独运行,其输出通过接入隔离电源后即可驱动相应的SIC MOS管进行工作。

2.2 动态栅偏实测验证

通过上述设计即可进行栅偏实验,使用SIC器件进行测试,其测试平台如图2-2所示

图2-2 测试平台

Figure 2-2 Test Platform

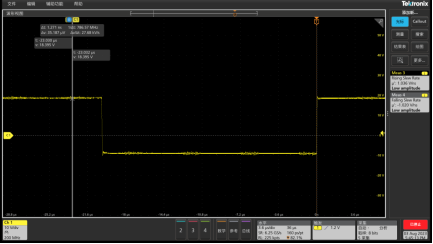

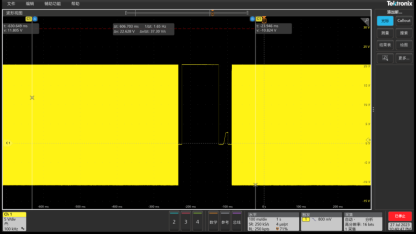

SIC的GS电压如图2-3所示

图2-3驱动输出电压

Figure 2-3 Drive Output Voltage

从图2-3不难看出,其输出的电压高电平为20V低电平为-10V,波形的频率为50KHZ,输出的波形无过冲,因为过冲可能影响器件的考核条件,使得器件更加容易击穿损坏,其上升沿(开通),下降沿(关断)的速率分别达到1.036V/ns以及1.020V/ns,满足AQG-324的要求。

3阈值电压测试方案

3.1 阈值电压原理

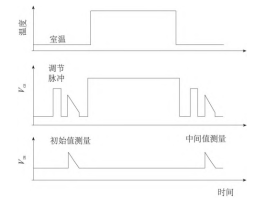

IEC 63275-1 ED1《半导体分立器件SiC MOSFET可靠性试验第1部分 : 偏压温度不稳定性试验》给出了 4 种阈值电压测试的示例,分别为恒流法 1( 恒定漏源电压 VDS 下测量阈值电压 )、恒流法2(VGS=VDS 下测量阈值电压 )、外推法和点测法,并规定标准使用者可选择任意一种方式对阈值电压进行测试,在此因为需要和动态栅偏进行同时测试,所以选择恒流法2进行验证。恒流法 2 的测试波形序列如图3-1所示。该方法同时扫描 VGS 与 VGS=VDS 下的 IDS,定义 VGS(th)下的IDS为 IDS(th)当扫描到的 IDS 达到IDS(th) 时,此时测量到的 VGS 便是 VGS(th)。

图3-1 恒流法波形序列

Figure 3-1 Waveform sequence of constant current method

使用继电器阵列以及恒流源设计相应控制检测回路,如图3-2所示。在进行栅偏时,继电器K1、K2闭合,给驱动供电,使驱动可以提供正负电压给MOS管GS工作,K3断开,K4闭合,K5断开,使其按照栅偏的要求进行栅偏实验。在需要进行阈值电压测试时,将K1、K2断开,是驱动芯片不工作,同时比克K3,使DS短路,断开K4闭合K5,接入恒流源,从而测得MOS管的阈值电压。恒流源使用TPS92612,其最大可以达到150MA,电流范围可以调整,带有控制端,从而可以在继电器完成相应逻辑后使能控制端让其工作,减少因为瞬间电流而造成的超调。

图3-2 阈值电压拓扑图

3-2 threshold voltage topology diagram

2.2阈值电压实测验证

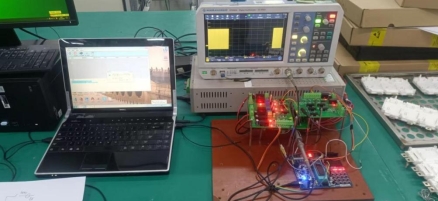

根据上述理论编写程序搭建测试平台如图3-3所示。

图3-3 测试平台

Figure 3-3 Test Platform

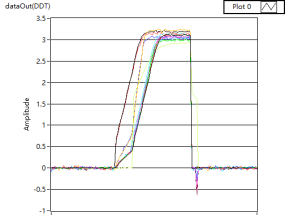

在栅偏完成后进行阈值电压测试,其波形如图3-4所示。

图3-4 栅偏阈值电压平台测试波形

Figure 3-4 Test waveform of gate bias threshold voltage platform

可以看出,在动态栅偏完成后即可开始阈值电压测试,其在一段直流电压应力后进行阈值电压测试。

4动态栅偏与阈值电压在线监测测试方案

因为示波器在测试系统中仅能监控1-4个MOS管的阈值电压波形,对于多个MOS管同时实验则无法进行实时测量,因此设计上位机采样系统进行采样设计,通过研华采样板卡以及labview程序对阈值电压实时采样,通过MCU控制采样触发,在阈值电压测试前2MS左右开始进行波形记录,在阈值电压测试结束后3MS左右停止波形记录,通过上位机可以一次捕捉12个MOS管的阈值电压波形,并保存图片以及相应的EXCEL数据,方便后期整理分析,其实验平台如图4-1所示,上位机采样图片如图4-2所示。

图4-1 实验平台

Figure 4-1 Experimental Platform

图4-2 上位机采样波形

Figure 4-2 Upper computer sampling waveform

总结

随着第三代半导体的发展,动态测试已经必不可少,本文设计了符合AQG324的动态栅偏的测试平台,同时将阈值电压与动态栅偏平台相结合,在栅偏过后即可进行阈值电压的测试,通过上位机平台实时处理数据,方便数据记录与分析,从而为SIC动态可靠性分析提供数据支持。

参考文献

[1] 孙肖子,邓建国,陈南等. 电子设计指南. 北京:高等教育出版社,2006. 30~31

[2] 闫美存 , 张秋 . SiC MOSFET 参数体系及测试方法研究 [J]. 信息技术与标准化 , 2021(9): 25-34.

[3] LELIS A J, HABERSAT D B, GREEN R, et al. Twoway tunneling model of oxide trap charging anddischarging in SiC MOSFETs[J]. Materials ScienceForum, 2012(717-720): 465-468.

[4] BASSLER M, AFANAS'EV V V, PENSL G, et al.Degradation of 6H-SiC MOS capacitors operatedat high temperatures[J]. MicroelectronicEngineering, 1999, 48(1-4): 257-260.

[5] MOGHADAM H A, DIMITRIJEV S, HAN J S, et al.Quantified density of active near interface oxidetraps in 4H-SiC MOS capacitors[J]. MaterialsScience Forum, 2016(858): 603-606.

[6] 池甜甜 . SiC MOSFET 阈值电压漂移特性的测试分析 [D]. 大连 : 大连理工大学 , 2021.

[7] YEN C T, HUNG C C, HUNG H T, et al. Negativebias temperature instability of SiC MOSFETinduced by interface trap assisted holetrapping[J]. Applied Physics Letters, 2016,108(1): 012106.

[8] JEITA. EDR-4713 化合物功率半导体器件可靠性测试方法指南 [S]. Tokyo:JEITA, 2017

作者简介:李博然(1995—),男,汉族,云南昆明,助理工程师,硕士研究生,广州广电计量检测集团股份有限公司,研究方向:电力电子技术。