武汉滨湖电子微波室 湖北省武汉市 430000

摘 要:本文对国产DDS芯片GM4912C与进口AD9914进行了功能、性能对比分析。设计了一种基于GM4912C的DDS模块并制作了样件。对样件进行了测试,并应用于某型号S波段频率综合器进行了进一步测试和验证。

关键词:相位噪声;SFDR;XC7A200T;GM4912C;

Abstract:This paper compares the domestic chip DDS GM4912C with the imported chip AD9914,and comparatice analysis of funciton performance is carried out。Designer a DDS module based on GM4912C,and made a sample.The sample was tested,it is also applied to a certain type of S-band frequency synthesizer.

Keys:phase noise;SFDR;XC7A200T;GM4912C.

1 引言

雷达波形产生系统在整个雷达系统中起着非常重要的作用,而线性调频信号是雷达系统中常用的一种脉冲压缩信号,其信号频率在信号持续期间连续变化。直接数字频率合成技术(DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术,与以往的各种传统领域合成技术相比,直接数字频率合成技术具有相对带宽、频率转换时间、相位连续、正交输出、高分辨率、以及集成化等明显优势。

DDS芯片广泛应用于频率源分系统的频率综合器、波形产生器等产品中。在波形产生器中,用于产生各种带宽、脉宽的线性调频波形。在频率综合器中,用于产生快速跳频、高信噪比、低相位噪声的跳频信号。为实现国产化波形产生器的设计功能,现采用国产FSK调试器GM4912C,搭配复旦微电子FPGA芯片JFM7K325T实现波形产生设计,通过技术指标对比,工程方案设计,方案功能设计等方面进行对比分析,能够实现国产化DDS的波形产生器的设计,本文设计了一种基于GM4912C的DDS模块,并应用于某型号S波段频率综合器中。本文对基于GM4912C的DDS模块,及此模块应用于某型号S波段频率综合器的测试结果进行了详细分析。

2 技术实现

本方案设计主要分析国产FSK调制器GM4912C替代AD9914的可行性以及优缺点的分析。AD9914是是一款3.5GSPS直接数字频率合成器,内置12位模数转换器,产品特性包括3.5Gsps内部时钟速度,集成12位DAC,频率调谐分辨率为190pHz,16位相位调谐分辨率,相比较AD9914功能,GM4912C为成都振芯科技有限公司产品,该产品是一款采样率最高为5GSPS的单通道FSK调制器,内部集成14位高速ADC,芯片可支持单凭率点、线性调频、FSK、PSK、ASK以及相干FSK等多种信号调制方式。[1]

FSK调制器GM4912C是一款采样率最高为5GSPS的单通道FSk调制器,内部集成14位高速DAC。芯片可支持多种信号调制方式。GM4912主要特点如下:1.48比特频率调谐精度;2.16比特相位调谐精度;3.14比特幅度调谐精度;4.可编程DAC电流输出;5.集成谐波对消功能,单频点应用时可提高杂散抑制能力。GM4912C主要实现单频点信号产生,信号调制以及多种模式的扫频信号产生。内部集成48比特DDS_CORE电路,采用16路并行的结构实现以降低芯片功耗。GM4912C内部主要包括串行SPI接口、内部配置寄存器组、线性扫描模块、SRAM相关模块、DESKEW模块及DAC模块等[2]。

2.1 相位噪声的对比

DDS模块工作时,输出信号fout的归一化相位噪声与参考时钟fclk的相位噪声满足20lg(fclk/fout)的优化关系。fclk的相位噪声较差时,fout的归一化相位噪声(normalized phase noise)远差于残余相位噪声(residual phasenoise),这时fout的测试相位噪声接近于归一化相位噪声。随着fclk的相位噪声质量提高,fout的归一化相位噪声逐渐接近于残余相位噪声。当fclk的相位噪声质量进一步提高,fout的归一化相位噪声低于残余相位噪声时,fout的测试相位噪声会无限接近于残余相位噪声,但不会低于残余相位噪声。AD9914可使用内部参考时钟模式或外部参考时钟模式。内部参考时钟模式通过内置的PLL实现。

采用外部参考时钟模式时,产生的时钟信号的相位噪声由外部时钟的相位噪声与AD9914的残余相位噪声共同决定。当外部参考时钟的相位噪声较低(归一化相位噪声低于残余相位噪声)时,产生的时钟信号的相位噪声约等于残余相位噪声。当外部参考时钟的相位噪声较高(归一化相位噪声高于残余相位噪声)时,产生的时钟信号的相位噪声约等于归一化相位噪声。

GM4912C同样可使用内部参考时钟和外部参考时钟。使用内部参考时钟时,内部PLL最高可产生5.0GHz的时钟,输出2.0GHz的时钟。通过对比分析,在电路设计的过程中,尽量使用外部参考时钟,且外部参考时钟由低相位噪声恒温晶振经直接频率合成技术产生,这样外部参考时钟的相位噪声较低,产生的时钟信号的归一化相位噪声远低于残余相位噪声,这样测试相位噪声可以无限接近于残余相位噪声,从而最大化的利用器件的性能。

2.2 无杂散动态范围SFDR的对比

无杂散动态范围(SFDR)是信号的均方根值与最差杂散信号的均方根值的比值。元器件的窄带SFDR反映了对近端杂散信号的抑制比。因信号的近端,尤其是10MHz频带内的杂散难以通过滤波器滤除,故窄带SFDR直接决定了输出信号的近端杂散抑制比。元器件的宽带SFDR反映了对远端杂散信号的抑制比,宽带SFDR对输出信号的杂散抑制比存在一定的影响,通过对输出端滤波器的选取,可进行一定程度的抑制。

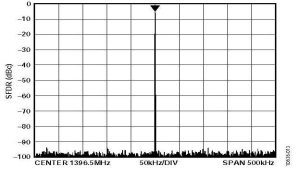

对国产GM4912C与进口AD9914的典型频点的窄带SFDR进行对比,如图1和图2所示,二者的1MHz窄带SFDR均可达到90dBc,性能接近。

图1 1MHz窄带SFDR,696.5MHz输出,3.5GHz时钟输入(AD9914)

图2 1MHz窄带SFDR,801.1MHz输出,5GHz时钟输入(GM4912C)

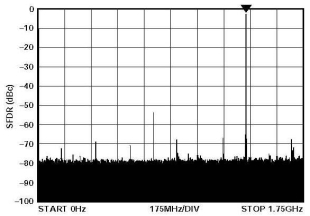

对国产GM4912C与进口AD9914的典型频点的宽带SFDR进行对比,如图1和图2所示。二者的宽带SFDR均在50dBc~55dBc。

图3 宽带SFDR,696.5MHz输出,3.5GHz时钟输入(AD9914)

图4 宽带SFDR,1100MHz输出,5GHz时钟输入(GM4912C)

根据对国产GM4912C与进口AD9914的窄带、宽带SFDR进行对比,二者的SFDR指标接近,无差距,故采用GM4912C搭配XC7A200T系列进行此次方案设计。

3 主要功能及技术指标要求

3.1 硬件设计

国产DDS波形产生器主要由逻辑处理模块、FSK调制模块、电源模块等组成,组成如图5 所示,工作原理为通过FPGA发送配置数据到FSK调制器进行配置,分别通过频率控制字、幅度控制字、相位控制字配置对应的寄存器,通过配置对应功能的寄存器输出需要的波形。

图5 波形产生组成框图

逻辑处理模块采用XC7A200T-2FBG484I进行处理,该芯片是一款Xilinx公司推出的FPGA芯片,属于Artix-7系列,拥有16825个LABs/CLBs和215360个逻辑单元,内置13140Kbit的RAM,具备强大的计算和存储能力,支持多种接口的通信标准。本方案设计使用S25FL256SAGMFI001作为Flash,通过60M有源晶振提供系统时钟,XC7A200T-2FBG484I芯片BANK电压主要通过不同输出电压类型的LDO设计供电部分。

GM4912C主要实现单频点信号产生,其信号输入输出电路图设计如下图所示。

图6 信号输入部分

图7 信号输出部分

GM4912C芯片内部主要功能包括数字电路,时钟产生电路,DAC电路,信号输入部分和输出部分均采用射频变压器TCM1-63AX+,为输入信号带宽为10-6000MHz,该射频变压器具有较低的插入损耗以及较好的回波损耗,首先将输入信号转换成差分信号后输入到GM4912C进行处理,输出部分通过射频变压器TCM1-63AX+后进行输出。

3.2 软件设计部分

本设计方案软件设计平台为Vivado 2018.3进行逻辑设计,本次程序设计主要分为三个步骤进行,首先根据需要输出的波形进行程序设计,主要包括对配置文件的逻辑编写,通过SPI接口对寄存器进行配置,SPI串口模块的基本功能是通过串口将配置数据写入到芯片内部的控制寄存器以实现对芯片工作模式与工作状态的实时控制。配置包括两个步骤:第一个阶段是配置指令字节,指令字节包括读写控制位,数据流控制位和寄存器地址。第二阶段是配置对应地址的寄存器数据,各寄存器的数据宽度与功能可查看寄存器列表。然后,根据时序设计,对逻辑代码进行仿真设计,主要查看复位信号,以及配置数据是否正确,最后调用vivado内IP核工具ILA对数据进行抓取验证。本次设计重点在于DDS内核的寄存器配置,以及SPI接口时序关系的设计,DDS基本结构图8所示,通过控制给相应功能的寄存器配置相应的频率相位幅度控制字,从而输出所需要的波形。

图8 DDS基本结构

图8 DDS基本结构

4 主要指标分析

4.1 相位噪声的测试结果及分析

一种基于GM4912C的DDS模块使用某型号S波段频率综合器产生的3200MHz时钟作为参考时钟。3200MHz参考时钟由100MHz低相位噪声恒温晶振经谐波发生器产生,再经窄带滤波、放大后得到。

3200MHz参考时钟的相位噪声测试曲线如图9所示。1kHz频偏处约-123.9dBc/Hz,1MHz频偏处约

-141.4dBcHz。

图9 GM4912C使用的外部参考时钟3200MHz的相位噪声

DDS模块产生的624.58MHz时钟信号的相位噪声测试曲线如图10所示。1kHz频偏处约-123.9dBc/Hz,1MHz频偏处约-141.4dBcHz。

图10 DDS模块产生的624.58MHz信号的相位噪声

根据图9和图10中3200MHz参考时钟、624.58MHz波形信号的测试相位噪声,计算出的3200MHz参考时钟产生624.58MHz的归一化相位噪声,以及GM4912C的数据手册给出的601MHz参考值分别如表4 所示。产生的624.58MHz时钟信号的测试相位噪声在1kHz、10kHz、100kHz频偏处均优于GM4912C数据手册给出的参考值,但差于归一化相位噪声,表明测试相位噪声达不到归一化相位噪声的值,已经基本发挥出了GM4912C的性能,测试值接近于GM4912C的残余相位噪声。624.58MHz时钟信号在1MHz频偏处的测试值较高,待模块的进一步优化。

表1 3200MHz参考时钟产生624.58MHz的归一化相位噪声和测试相位噪声

3200MHz参考时钟 的测试相位噪声 | 3200MHz参考时钟 产生624.58MHz 的归一化相位噪声 | GM4912C模块产生 624.58MHz 测试相位噪声 | 601.1MHz (GM4912C数据 手册的参考值) | |

@1kHz频偏 | -123.9dBc/Hz | -138.1dBc/Hz | -131.3dBc/Hz | -119.5dBc/Hz |

@10kHz频偏 | -128.4dBc/Hz | -142.6dBc/Hz | -134.4dBc/Hz | -127.5dBc/Hz |

@100kHz频偏 | -133.0dBc/Hz | -147.2dBc/Hz | -136.4dBc/Hz | -129.5dBc/Hz |

@1MHz频偏 | -141.4dBc/Hz | -155.6dBc/Hz | -137.1dBc/Hz | -145.5dBc/Hz |

如表1 和表2 所示为3200MHz参考时钟产生624.58MHz的测试相位噪声,与AD9914在696MHz的残余相位噪声的对比。根据数据对比,在1kHz频偏处,GM4912C差约2.7dB,较为接近。在10kHz频偏及更远端,差距更明显。需进一步测试分析,是GM4912C器件的残余相位噪声的影响,或是电源等因素造成的影响。

表2 GM4912C模块产生的624.58MHz的测试相位噪声与AD9914残余相位噪声的对比

696MHz (AD9914残余相位噪声) | GM4912C模块产生624.58MHz 的测试相位噪声 | |

@1kHz频偏 | -134dBc/Hz | -131.3dBc/Hz |

@10kHz频偏 | -142dBc/Hz | -134.4dBc/Hz |

@100kHz频偏 | -148dBc/Hz | -136.4dBc/Hz |

@1MHz频偏 | -150dBc/Hz | -137.1dBc/Hz |

4.2 近端杂散的测试结果

下图所示为GM1912C模块产生的624.58MHz信号的1MHz和10MHz近端杂散测试图。1MHz带内和10MHz带内的杂散抑制比均大于80dBc,基本符合元器件的窄带SFDR指标。

|

|

图11 DDS模块产生的624.58MHz信号的近端杂散

4.3 应用于某型号S波段频率综合器的测试结果

基于GM4912C的DDS模块应用于某型号S波段频率综合器进行了测试。由GM4912C产生624.58MHz的时钟信号,与S波段频踪产生的4200MHz混频,产生频率为3575.42MHz的S波段一本振。

混频后的输出相位噪声功率谱密度为两个输入信号相位噪声功率谱密度之和,用公式可表示为:

![]() ......................................(式4.1)

......................................(式4.1)

如图12所示,为某型号S波段频率综合器产生的4200MHz本振的测试相位噪声。

图12 应用于S波段频综时混频的4200MHz参考本振

如图13所示,为应用于S波段频率综合器产生的3575.42MHz的S波段一本振的测试相位噪声1kHz频偏处相位噪声。

图13 应用于S波段频综产生的3575.42MHz时钟的相位噪声

图11中624.58MHz波形信号,图12中4200MHz时钟,图13中产生的3575.42MHz时钟的测试相位噪声,以及由公式4.1计算出的4200MHz与624.58MHz混频后的相位噪声理论值在100Hz、1kHz、10kHz、100kHz、1MHz频偏处的值分别如表6 所示。混频产生的3575.42MHz时钟与混频理论值在100Hz、1kHz、10kHz、100kHz频偏处相差分别为1.2dBc、0dBc、0.7dBc、0.4dBc,考虑测试过程带来的误差,可认为测试值与公式4.1的理论值相符合。

表3 混频前后的相位噪声对比

624.58MHz | 4200MHz 混频本振 | 3575.42MHz S波段一本振 | 混频 理论值 | |

@100Hz频偏 | -111.8dBc/Hz | -96.9dBc/Hz | -98.0dBc/Hz | -96.8dBc/Hz |

@1kHz频偏 | -131.3dBc/Hz | -121.5dBc/Hz | -121.0dBc/Hz | -121.0dBc/Hz |

@10kHz频偏 | -134.4dBc/Hz | -126.3dBc/Hz | -126.4dBc/Hz | -125.7dBc/Hz |

@100kHz频偏 | -136.4dBc/Hz | -131.3dBc/Hz | -129.7dBc/Hz | -130.1dBc/Hz |

@1MHz频偏 | -137.1dBc/Hz | -137.7dBc/Hz | -131.9dBc/Hz | -134.4dBc/Hz |

4.4 测试结果分析及小结

根据对GM4912C产生的624.58MHz信号的测试数据,应用于某型号S波段频率综合器的测试数据,以及与进口AD9914的理论值的对比。GM4912C的1KHz频偏的近端相位噪声接近于AD9914,但远端相位噪声与AD9914存在一定的差距。应用于某型S频综后,验证了公式1即混频过程的相位噪声计算。在频率综合器的设计过程中,通过对频点的合理分配,可以避开GM4912C在远端与AD9914的相位噪声的差距。GM4912C的近端SFDR与AD9914相比则无差距。

5 总结

本文对国产DDS芯片GM4912C与进口AD9914进行了功能、性能对比分析。设计了一种基于GM4912C的DDS模块并制作了样件。对样件进行了测试,并应用于某型号S波段频率综合器进行了进一步测试和验证。

根据测试结果和对比数据,GM4912C的近端SFDR与AD9914相比无差距,GM4912C的1kHz频偏的近端相位噪声接近于AD9914,但10kHz以外的远端相位噪声存在差距。在频率综合器的设计过程中通过频点的合理分配,可避开这一段差距,达到使用需求。

本文介绍了基于国产FSK调制器的波形产生器的主要功能和技术指标,由于项目处于研发初步阶段,因此先行搭建波形产生器整体框架,对频率规划、信号质量等做了初步考虑,为项目后续开展做好准备。

参 考 文 献

[1] GM4192C 4GHz FSK调制器数据手册 成都振芯科技股份有限公司 2015.5

[2] 3.5GSPS直接数字频率合成器内置12位数模转换器AD9914数据手册 ADI 2012.7

[3] 雷达原理 丁鹭飞 耿富录 西安电子科技大学出版社 2002

![]()